本技术涉及测试,特别是涉及一种fpga测试数据采集方法、fpga及装置。

背景技术:

1、相关技术中,fpga(field programmable gate array,现场可编程门阵列)开发人员在对fpga进行调试定位时需要依赖fpga厂商提供的工具抓取fpga内部的信号波形,作为测试数据。但是使用以上工具时需要使用jtag(join test action group,联合测试工作组)加载盒子,jtag加载盒子与fpga相连。并且,接收测试数据,并对测试数据进行处理生成测试结果的调试机上还需要安装eda(electronic design automation,电子设计自动化)软件。调试机与jtag之间通过有线或无线网络通信连接,进行数据交互。

2、参见图1,为相关技术中的一种fpga测试场景示意图。图中包含调试机、jtag加载盒子与fpga。图中示出了三者之间的连接关系。

3、由此可见,相关技术中进行fpga测试数据的采集需要专用的jtag加载盒子和eda软件,导致fpga调试的软硬件成本较大。

技术实现思路

1、本技术实施例的目的在于提供一种fpga测试数据采集方法、fpga及装置,以降低fpga的调试成本。具体技术方案如下:

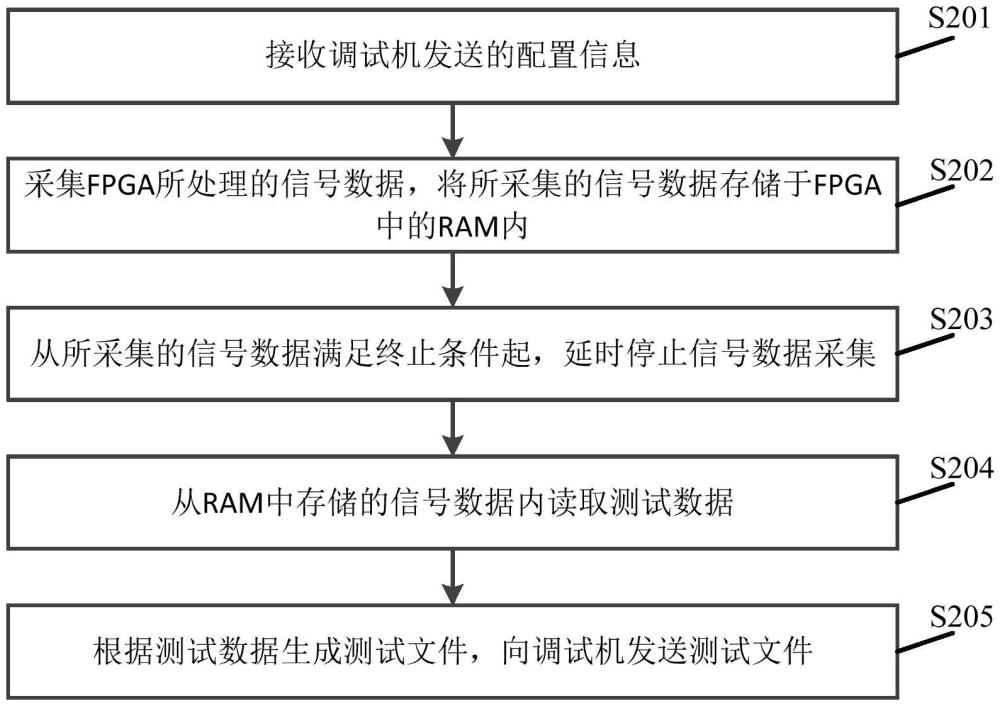

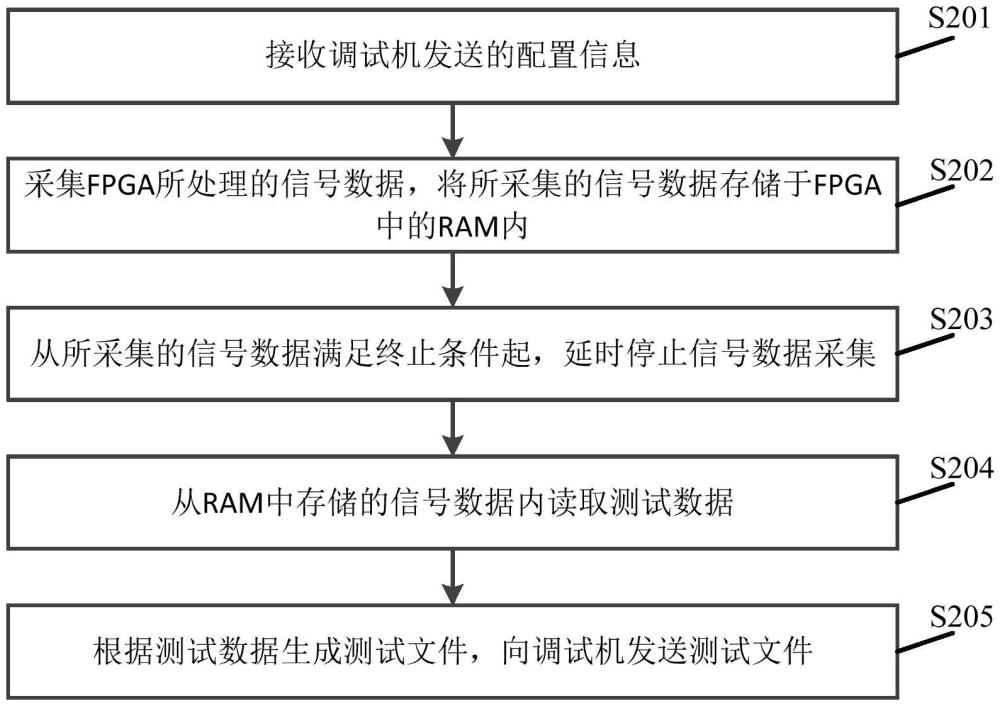

2、在本技术实施例的第一方面,首先提供了一种fpga测试数据采集方法,应用于fpga,所述fpga与调试机相连,所述方法包括:

3、接收调试机发送的配置信息;其中,所述配置信息表示信号数据采集的终止条件、采样深度;

4、采集所述fpga所处理的信号数据,将所采集的信号数据存储于所述fpga中的随机存储器ram内;

5、从所采集的信号数据满足所述终止条件起,延时停止信号数据采集;

6、从所述ram中存储的信号数据内读取测试数据;其中,所述测试数据为连续采集的、在所述采样深度个时钟周期中采集的信号数据,所述测试数据中包含在满足所述终止条件的时钟周期中采集的信号数据;

7、根据所述测试数据生成测试文件,向所述调试机发送所述测试文件。

8、在一种可能的实施例中,所述配置信息还表示触发位置,所述触发位置为满足所述终止条件的时钟周期中采集的信号数据在所述测试数据中的次序;

9、所述在所采集的信号数据满足所述终止条件之后,延时停止信号数据采集,包括:

10、从所采集的信号数据满足所述终止条件起,继续在目标时钟周期中采集有效信号数据后停止采集;其中,所述目标时钟周期的数量为所述采样深度与所述触发位置之差;

11、所述从所述ram中存储的信号数据内读取测试数据,包括:

12、从所述ram中存储的信号数据内读取包含所述有效信号数据的测试数据。

13、在一种可能的实施例中,在一个时钟周期中采集的信号数据的数据量大于一个ram的数据位宽的情况下,所述将所采集的信号数据存储于所述fpga中的随机存储器ram内,包括:

14、将同一时钟周期采集的信号数据中的不同部分,分别存储于所述fpga中的多个ram的次序相同的行中;

15、所述从所述ram中存储的信号数据内读取测试数据,包括:

16、分别从所述多个ram中读取数据;

17、将所读取的所述多个ram中的数据组合为测试数据,其中,每一测试数据由所述多个ram中次序相同的行内记载的数据组成。

18、在一种可能的实施例中,所述终止条件包括一个或多个触发条件;

19、在所述终止条件包括多个触发条件时,相邻的触发条件之间存在逻辑关系。

20、在一种可能的实施例中,所述触发条件包括:信号值、触发门限、所述信号值和触发门限之间的关系符。

21、在本技术实施例的第二方面,还提供了一种fpga测试数据采集方法,应用于调试机,所述调试机与现场可编程门阵列fpga相连,所述方法包括:

22、获取配置信息;其中,所述配置信息表示信号数据采集的终止条件、采样深度;

23、向所述fpga发送配置信息,以使得所述fpga根据所述配置信息采集所述fpga处理的信号数据,并生成包含所采集的信号数据中测试数据的测试文件,向所述调试机发送所述测试文件;其中,所述测试数据为连续采集的、在所述采样深度个时钟周期中采集的信号数据,所述测试数据中包含在满足所述终止条件的时钟周期中采集的信号数据;

24、接收所述fpga发送的测试文件。

25、在一种可能的实施例中,所述配置信息还表示触发位置,所述触发位置为所述fpga在满足所述终止条件的时钟周期中采集的信号数据在所述测试数据中的次序。

26、在一种可能的实施例中,在所述接收所述fpga发送的测试文件之后,还包括:

27、在信号波形显示界面中显示所述测试文件表示的信号波形。

28、在一种可能的实施例中,所述获取配置信息,包括:

29、接收配置信息输入信号;其中,所述配置信息输入信号用于指示待生成的配置信息中包含的参数的取值;

30、根据所述配置信息输入信号,生成配置信息。

31、在一种可能的实施例中,所述终止条件包括一个或多个触发条件;

32、在所述终止条件包括多个触发条件时,相邻的触发条件之间存在逻辑关系。

33、在一种可能的实施例中,所述触发条件包括:信号值、触发门限、所述信号值和触发门限之间的关系符。

34、在本技术实施例的第三方面,还提供了一种fpga,所述fpga与调试机相连,所述fpga用于执行以下操作:

35、接收调试机发送的配置信息;其中,所述配置信息表示信号数据采集的终止条件、采样深度;

36、采集所述fpga所处理的信号数据,将所采集的信号数据存储于所述fpga中的随机存储器ram内;

37、从所采集的信号数据满足所述终止条件起,延时停止信号数据采集;

38、从所述ram中存储的信号数据内读取测试数据;其中,所述测试数据为连续采集的、在所述采样深度个时钟周期中采集的信号数据,所述测试数据中包含在满足所述终止条件的时钟周期中采集的信号数据;

39、根据所述测试数据生成测试文件,向所述调试机发送所述测试文件。

40、在一种可能的实施例中,所述配置信息还表示触发位置,所述触发位置为满足所述终止条件的时钟周期中采集的信号数据在所述测试数据中的次序;所述fpga具体用于:

41、从所采集的信号数据满足所述终止条件起,继续在目标时钟周期中采集有效信号数据后停止采集;其中,所述目标时钟周期的数量为所述采样深度与所述触发位置之差;

42、所述fpga具体用于:

43、从所述ram中存储的信号数据内读取包含所述有效信号数据的测试数据。

44、在一种可能的实施例中,在一个时钟周期中采集的信号数据的数据量大于一个ram的数据位宽的情况下,所述fpga具体用于:

45、将同一时钟周期采集的信号数据中的不同部分,分别存储于所述fpga中的多个ram的次序相同的行中;

46、所述fpga具体用于:

47、分别从所述多个ram中读取数据;

48、将所读取的所述多个ram中的数据组合为测试数据,其中,每一测试数据由所述多个ram中次序相同的行内记载的数据组成。

49、在一种可能的实施例中,所述终止条件包括一个或多个触发条件;

50、在所述终止条件包括多个触发条件时,相邻的触发条件之间存在逻辑关系。

51、在一种可能的实施例中,所述触发条件包括:信号值、触发门限、所述信号值和触发门限之间的关系符。

52、在本技术实施例的第四方面,还提供了一种调试机,所述调试机与现场可编程门阵列fpga相连,所述调试机包括存储器,收发机,处理器:

53、存储器,用于存储计算机程序;收发机,用于在所述处理器的控制下收发数据;处理器,用于读取所述存储器中的计算机程序并执行以下操作:

54、获取配置信息;其中,所述配置信息表示信号数据采集的终止条件、采样深度;

55、向所述fpga发送配置信息,以使得所述fpga根据所述配置信息采集所述fpga处理的信号数据,并生成包含所采集的信号数据中测试数据的测试文件,向所述调试机发送所述测试文件;其中,所述测试数据为连续采集的、在所述采样深度个时钟周期中采集的信号数据,所述测试数据中包含在满足所述终止条件的时钟周期中采集的信号数据;

56、接收所述fpga发送的测试文件。

57、在一种可能的实施例中,所述配置信息还表示触发位置,所述触发位置为所述fpga在满足所述终止条件的时钟周期中采集的信号数据在所述测试数据中的次序。

58、在一种可能的实施例中,所述处理器,还用于:

59、在信号波形显示界面中显示所述测试文件表示的信号波形。

60、在一种可能的实施例中,所述处理器,具体用于:

61、接收配置信息输入信号;其中,所述配置信息输入信号用于指示待生成的配置信息中包含的参数的取值;

62、根据所述配置信息输入信号,生成配置信息。

63、在一种可能的实施例中,所述终止条件包括一个或多个触发条件;

64、在所述终止条件包括多个触发条件时,相邻的触发条件之间存在逻辑关系。

65、在一种可能的实施例中,所述触发条件包括:信号值、触发门限、所述信号值和触发门限之间的关系符。

66、在本技术实施例的第五方面,还提供了一种fpga测试数据采集装置,应用于现场可编程门阵列fpga,所述fpga与调试机相连,所述装置包括:

67、信息接收模块,用于接收调试机发送的配置信息;其中,所述配置信息表示信号数据采集的终止条件、采样深度;

68、第一采集模块,用于采集所述fpga所处理的信号数据,将所采集的信号数据存储于所述fpga中的随机存储器ram内;

69、第二采集模块,用于从所采集的信号数据满足所述终止条件起,延时停止信号数据采集;

70、数据读取模块,用于从所述ram中存储的信号数据内读取测试数据;其中,所述测试数据为连续采集的、在所述采样深度个时钟周期中采集的信号数据,所述测试数据中包含在满足所述终止条件的时钟周期中采集的信号数据;

71、文件发送模块,用于根据所述测试数据生成测试文件,向所述调试机发送所述测试文件。

72、在一种可能的实施例中,所述配置信息还表示触发位置,所述触发位置为满足所述终止条件的时钟周期中采集的信号数据在所述测试数据中的次序;

73、所述第二采集模块,具体用于:

74、从所采集的信号数据满足所述终止条件起,继续在目标时钟周期中采集有效信号数据后停止采集;其中,所述目标时钟周期的数量为所述采样深度与所述触发位置之差;

75、所述数据读取模块,具体用于:

76、从所述ram中存储的信号数据内读取包含所述有效信号数据的测试数据。

77、在一种可能的实施例中,在一个时钟周期中采集的信号数据的数据量大于一个ram的数据位宽的情况下,所述第一采集模块,具体用于:

78、将同一时钟周期采集的信号数据中的不同部分,分别存储于所述fpga中的多个ram的次序相同的行中;

79、所述数据读取模块,具体用于:

80、分别从所述多个ram中读取数据;

81、将所读取的所述多个ram中的数据组合为测试数据,其中,每一测试数据由所述多个ram中次序相同的行内记载的数据组成。

82、在一种可能的实施例中,所述终止条件包括一个或多个触发条件;

83、在所述终止条件包括多个触发条件时,相邻的触发条件之间存在逻辑关系。

84、在一种可能的实施例中,所述触发条件包括:信号值、触发门限、所述信号值和触发门限之间的关系符。

85、在本技术实施例的第六方面,还提供了一种fpga测试数据采集装置,应用于调试机,所述调试机与现场可编程门阵列fpga相连,所述装置包括:

86、信息获取模块,用于获取配置信息;其中,所述配置信息表示信号数据采集的终止条件、采样深度;

87、信息发送模块,用于向所述fpga发送配置信息,以使得所述fpga根据所述配置信息采集所述fpga处理的信号数据,并生成包含所采集的信号数据中测试数据的测试文件,向所述调试机发送所述测试文件;其中,所述测试数据为连续采集的、在所述采样深度个时钟周期中采集的信号数据,所述测试数据中包含在满足所述终止条件的时钟周期中采集的信号数据;

88、文件接收模块,用于接收所述fpga发送的测试文件。

89、在一种可能的实施例中,所述配置信息还表示触发位置,所述触发位置为所述fpga在满足所述终止条件的时钟周期中采集的信号数据在所述测试数据中的次序。

90、在一种可能的实施例中,在所述文件接收模块接收所述fpga发送的测试文件之后,还包括:

91、波形显示模块,用于在信号波形显示界面中显示所述测试文件表示的信号波形。

92、在一种可能的实施例中,所述信息获取模块,具体用于:

93、接收配置信息输入信号;其中,所述配置信息输入信号用于指示待生成的配置信息中包含的参数的取值;

94、根据所述配置信息输入信号,生成配置信息。

95、在一种可能的实施例中,所述终止条件包括一个或多个触发条件;

96、在所述终止条件包括多个触发条件时,相邻的触发条件之间存在逻辑关系。

97、在一种可能的实施例中,所述触发条件包括:信号值、触发门限、所述信号值和触发门限之间的关系符。

98、在本技术实施的又一方面,还提供了一种计算机可读存储介质,所述计算机可读存储介质内存储有计算机程序,所述计算机程序被处理器执行时实现上述第一方面或第二方面任一所述的方法步骤。

99、本技术实施例有益效果:

100、本技术实施例提供的fpga测试数据采集方法,fpga在接收到调试机发送的配置信息的情况下,采集fpga所处理的信号数据,将所采集的信号数据存储于fpga中的ram内。由于配置信息表示信号数据采集的终止条件、采样深度,fpga从所采集的信号数据满足终止条件起,延时停止信号数据采集,并从ram中存储的信号数据内读取测试数据,根据测试数据生成测试文件,向调试机发送测试文件,从而完成fpga测试数据的采集过程。

101、此外,由于fpga测试数据的采集过程中,fpga与调试机相连,不需要专用的jtag加载盒子和eda软件,省去了专用的jtag加载盒子和eda软件的成本,从而降低了fpga的调试成本。

102、当然,实施本技术的任一产品或方法并不一定需要同时达到以上所述的所有优点。