用于高速数据和低速指令信号传输的接收器及传输器的制作方法

用于高速数据和低速指令信号传输的接收器及传输器

1.原申请案的申请日是2021年3月17日,原申请案的申请号是202110286724.7,且原申请案的发明名称是“用于高速数据和低速指令信号传输的接收器及传输器”。

技术领域

2.本发明涉及一种信号传输系统,尤其涉及一种具有接收器和传输器且具备高速数据及低速指令信号传输能力的信号传输系统。

背景技术:

3.在传统电路板上的信号传输系统中,当电源启动之后,主机端装置应发送指令信号以控制从属端装置开始运作,接着,数据信号可在主机端装置和从属端装置之间传送。

4.信号传输系统存在多种常见的信号传输方法。在一示例中,指令信号是利用与高速数据速率相同的信号速率进行传输,以实现高速序列传输,然而,在指令信号被正确接收以前,接收器可能无法完成设定以正常接收高速指令信号。在另一实施例中,也可将指令信号独立传送,但其存在路径数较多和硬体设置上的缺点。或者,从属端装置可被提供给固定的设定值,但此设定值无法在不同情况下弹性地进行调整。

5.因此,实有必要提出一种新式的信号传输系统,其具备传送低速指令信号和高速数据信号的能力。

技术实现要素:

6.因此,本发明的主要目的即在于提供一种具有接收器和传输器且具备高速数据及低速指令信号传输能力的信号传输系统。

7.本发明的一实施例公开了一种接收器,用来接收一串行指令信号及一串行数据信号。该接收器包括一第一时钟数据恢复(clock and data recovery,cdr)电路、一控制电路及一第二时钟数据恢复电路。该第一时钟数据恢复电路可用来处理该串行指令信号,以产生一时钟信号。该控制电路耦接于该第一时钟数据恢复电路,可用来根据该串行指令信号及来自于该第一时钟数据恢复电路的该时钟信号,产生一控制信号。该第二时钟数据恢复电路耦接于该控制电路,可用来根据来自于该控制电路的该控制信号,对该串行数据信号进行处理。

8.本发明的另一实施例公开了一种传输器,用来传送一串行指令信号及一串行数据信号。该传输器包括一序列化器(serializer)及一多路复用器(multiplexer)。该序列化器可用来产生该串行数据信号。该多路复用器耦接于该序列化器,用来选择输出该串行指令信号或该串行数据信号。

9.本发明的另一实施例公开了一种接收器,其可通过多个信道耦接于一传输器,用来接收来自于该传输器的一串行指令信号及一串行数据信号。该接收器包括一控制电路及一第一时钟数据恢复电路。该控制电路可用来通过该多个信道中的一第一信道接收该串行指令信号,并通过该多个信道中的一第二信道接收一时钟信号,以根据该串行指令信号及

该时钟信号来产生一第一控制信号。该第一时钟数据恢复电路耦接于该控制电路,可用来根据来自于该控制电路的该第一控制信号,对该串行数据信号进行处理。

10.本发明的另一实施例公开了一种传输器,其可通过多个信道耦接于一接收器,用来传送一串行指令信号及一串行数据信号至该接收器。该传输器包括一序列化器及一第一多路复用器。该序列化器可用来产生该串行数据信号。该第一多路复用器耦接于该序列化器,可用来选择传送该串行指令信号或该串行数据信号至该多个信道中的一第一信道。其中,对应于该串行指令信号的一时钟信号是通过该多个信道中的一第二信道进行传送。

附图说明

11.图1至图3为一信号传输系统的示意图。

12.图4及图5为本发明实施例一信号传输系统的示意图。

13.图6示出了数种可用于信号传输系统的示例性曼彻斯特编码法。

14.图7为本发明实施例另一信号传输系统的示意图。

15.图8为本发明实施例又一信号传输系统的示意图。

16.其中,附图标记说明如下:

17.10、20、30、40、50、70、80信号传输系统

18.100、200、300、400、500、700、800传输器

19.102、202、302、402、502、702、802序列化器

20.104、204、214、304、404、504、704_1、输出缓冲器

21.704_2、804

22.150、250、350、450、550、750、850接收器

23.152、252、352、452、552、752、852终端电路

24.154、254、354、454、554、754、854均衡器

25.156、256、356、456_1、456_2、556_1、时钟数据恢复电路756、856

26.158、258、358、458、558、758、858控制电路

27.160、260、360、460、560、760、860去序列化器

28.162分频器

29.ch1、ch2、cha、chb信道

30.406、506、706、806多路复用器

31.508曼彻斯特编码器

32.510异或门

33.556_2曼彻斯特解码器

34.p1、p2收发器对

具体实施方式

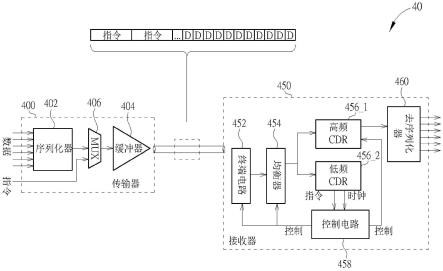

35.请参考图1,图1为一信号传输系统10的示意图。如图1所示,信号传输系统10包括一传输器100及一接收器150。传输器100可以是位于电路板上的一主机端装置(如系统处理器),其包括一序列化器(serializer)102及一输出缓冲器104。来自于系统处理器中数位电路的串行指令信号及串行数据信号可通过传输器100进行传送。序列化器102可对指令信号

和数据信号执行并行到串行转换,以产生序列化的指令信号和数据信号。输出缓冲器104则用来输出指令信号和数据信号至接收器150。

36.接收器150可以是位于电路板上的一从属端装置(如功能性集成电路(integrated circuit,ic)),其包括一终端电路152、一均衡器(equalizer)154、一时钟数据恢复(clock and data recovery,cdr)电路156、一控制电路158、一去序列化器(deserializer)160及一分频器(frequency divider)162。终端电路152通常设置于一高速传输系统,用来进行阻抗匹配,其可包括终端电阻或任何可产生阻抗的其它类似的电路组件。均衡器154可用来补偿信道上产生的信号损失。时钟数据恢复电路156可用来取出内嵌于所接收指令信号及数据信号的时钟信号。接着,时钟信号可借由分频器162进行分割,以产生另一具有较低频率的时钟信号,以提供给控制电路158使用。控制电路158可以是设置于集成电路内部的数位电路,其可用来控制接收器150中各电路方块的各项运作。去序列化器160可用来对数据信号执行串行到并行转换,从而以并行形式输出数据信号至后续电路。

37.如图1所示,传输器100可传送串行指令信号(以c表示)和串行数据信号(以d表示)至接收器150。需注意,指令信号是在数据信号之前传送和接收。指令信号可用来起始或设定接收器150中的电路方块,例如终端电路152、均衡器154及时钟数据恢复电路156等。因此,当指令信号成功被接收和处理之后,代表接收器150中的电路方块已准备好接收和处理高速数据信号。在此例中,指令信号和数据信号是通过相同信道进行高速传送。然而,接收器150的电路方块需根据指令信号来进行起始或设定,在尚未完成初始化之前,这些电路方块无法成功接收并处理高速的指令信号。

38.请参考图2,图2为一信号传输系统20的示意图。如图2所示,信号传输系统20包括一传输器200及一接收器250。传输器200包括一序列化器202及一输出缓冲器204,其运作方式分别类似于图1中的序列化器102及输出缓冲器104,故不再详述于此。接收器250包括一终端电路252、一均衡器254,一时钟数据恢复电路256,一控制电路258及一去序列化器260,其运作方式也分别类似于图1中的终端电路152、均衡器154、时钟数据恢复电路156、控制电路158及去序列化器160,故不再详述于此。

39.在信号传输系统20中,数据信号是通过一主要信道ch1传送,指令信号则通过相异于主要信道ch1的一指令信道ch2传送。指令信号是以低速进行传送,使得控制电路258得以顺利接收并处理指令信号。在此例中,传输器200包括另一输出缓冲器214,用来输出指令信号至信道ch2。由于指令信号是在低速下传送,其可直接传送至控制电路258而无须通过终端电路252、均衡器254及时钟数据恢复电路256的处理。在信号传输系统20中,指令信号和数据信号是通过不同信道传送,且指令信号是在低速下传送,可解决信号传输系统10中高速指令信号无法顺利被接收或处理的问题。然而,信号传输系统20需设置额外的信道,其伴随着成本的提高及信号偏移(signal skew)的问题。

40.请参考图3,图3为一信号传输系统30的示意图。如图3所示,信号传输系统30包括一传输器300及一接收器350。传输器300包括一序列化器302及一输出缓冲器304,其运作方式分别类似于图1中的序列化器102及输出缓冲器104,故不再详述于此。接收器350包括一终端电路352、一均衡器354、一时钟数据恢复电路356、一控制电路358及一去序列化器360,其运作方式也分别类似于图1中的终端电路152、均衡器154、时钟数据恢复电路156、控制电路158及去序列化器160,故不再详述于此。

41.在图3的示例中,指令信号可通过一输入端口传送至控制电路358,此输入端口不同于数据信号的接收端口,因此需要更多的端口数量,造成更高的电路成本。

42.请参考图4,图4为本发明实施例一信号传输系统40的示意图。如图4所示,信号传输系统40包括一传输器400及一接收器450。传输器400包括一序列化器402及一输出缓冲器404,其运作方式分别类似于图1中的序列化器102及输出缓冲器104,故不再详述于此。接收器450包括一终端电路452、一均衡器454、一控制电路458及一去序列化器460,其运作方式也分别类似于图1中的终端电路152、均衡器154、控制电路158及去序列化器160,故不再详述于此。

43.在此例中,低速指令信号和高速数据信号是通过相同信道传送,且指令信号是在数据信号之前传送和接收,使得接收器450中的电路方块可先由指令信号进行初始化,接着在成功初始化之后接收高速数据信号。因此,信号传输系统40不需要额外的端口或信道,可避免信号传输系统40中的信号偏移问题。

44.传输器400还包括一多路复用器(multiplexer,mux)406,耦接于序列化器402及输出缓冲器404之间。多路复用器406可用来选择传送指令信号或数据信号至输出缓冲器404。在此例中,数据信号和指令信号是通过不同输入端传送至传输器400。更明确来说,数据信号是由序列化器402进行序列化,而指令信号是直接传送至多路复用器406。借由多路复用器406的控制,数据信号和指令信号可合并后以串行方式输出至相同信道。

45.为了同时处理低速指令信号和高速数据信号,接收器450包括一高频时钟数据恢复电路456_1及一低频时钟数据恢复电路456_2。高频时钟数据恢复电路456_1可用来处理高速数据信号,低频时钟数据恢复电路456_2可用来处理低速指令信号。由于指令信号是在数据信号之前进行接收,因此,低频时钟数据恢复电路456_2可在数据信号被接收之前先开始处理指令信号。根据所接收的指令信号,低频时钟数据恢复电路456_2可产生一时钟信号,并输出时钟信号和指令信号至控制电路458。控制电路458即可发送控制信号至终端电路452,均衡器454及/或高频时钟数据恢复电路456_1以起始或设定这些电路方块。如此一来,根据所接收的控制信号,这些电路方块即可做好接收和处理高速数据信号的准备。

46.在此例中,串行指令信号为低速指令信号,而串行数据信号为高速数据信号。指令信号和数据信号可通过任何频率或信号速率进行传送。只要数据信号的数据速率大于指令信号的信号速率,所使用的传输机制以及相关的传输器和接收器都属于本发明的范畴。

47.值得注意的是,图4中的接收器450需要两个时钟数据恢复电路分别用来处理不同频率的信号,造成硬体成本的增加。在一实施例中,可采用大范围的时钟数据恢复电路来取代高频时钟数据恢复电路456_1及低频时钟数据恢复电路456_2。此大范围的时钟数据恢复电路可用来处理较大频率范围的信号。一般来说,数据信号的数据速率是指令信号的信号速率的数倍,在较大的频率差距之下,所需的时钟数据恢复电路的复杂度和困难度也随之而大幅提升。

48.为了简化时钟数据恢复电路的设计并降低接收器的电路成本,在一实施例中,可根据一类曼彻斯特编码(manchester-like encoding)方案来传送指令信号。类曼彻斯特编码方案包括g.e.汤玛斯曼彻斯特编码(g.e.thomas manchester encoding)、ieee 802.3曼彻斯特编码(ieee 802.3manchester encoding)、以及差分曼彻斯特编码(differential manchester encoding),而不限于此。为求简化,下文将这些类曼彻斯特编码统称为曼彻斯

特编码。若指令信号是通过曼彻斯特编码来处理,则低频时钟数据恢复电路456_2可以是一曼彻斯特解码器,相较于一般时钟数据恢复电路而言,曼彻斯特解码器更为简化且便宜。

49.请参考图5,图5为本发明实施例一信号传输系统50的示意图。如图5所示,信号传输系统50包括一传输器500及一接收器550。传输器500包括一序列化器502、一输出缓冲器504及一多路复用器506,其运作方式分别类似于图4中的序列化器402、输出缓冲器404及多路复用器406,故不再详述于此。接收器550包括一终端电路552、一均衡器554、一时钟数据恢复电路556_1、一控制电路558及一去序列化器560,其运作方式分别类似于图4中的终端电路452、均衡器454、高频时钟数据恢复电路456_1、控制电路458及去序列化器460,故不再详述于此。

50.传输器500还包括一曼彻斯特编码器508,曼彻斯特编码器508耦接于多路复用器506,其可根据曼彻斯特编码法,对指令信号进行编码。曼彻斯特编码法使得传送至接收器550的指令信号携带有时钟信息;对应地,接收器550可取出时钟信号,而无须使用复杂的时钟数据恢复电路以及额外的时钟端口,可降低接收器550的电路面积和耗电。在另一实施例中,曼彻斯特编码器508及多路复用器506也可包含在序列化器502中,或者与序列化器502互相整合。

51.详细来说,曼彻斯特编码器508可包括用来接收指令信号的一第一输入端、用来接收时钟信号的一第二输入端、以及一输出端。时钟信号可设定为具有相同于指令信号的频率,使得曼彻斯特编码变得可行。当指令信号借由时钟信号进行编码之后,可通过输出端来输出指令信号。在一实施例中,曼彻斯特编码器508可包括一异或门(xor gate)510,如图5所示。异或门510可对原始指令信号和时钟信号执行异或运算,以产生编码后的指令信号。

52.图6示出了数种可用于信号传输系统50的示例性曼彻斯特编码法。如图6所示,可行的曼彻斯特编码法包括g.e.汤玛斯曼彻斯特编码、ieee 802.3曼彻斯特编码、以及差分曼彻斯特编码。根据g.e.汤玛斯曼彻斯特编码,时钟信号的上升缘与指令信号的转态时间点对齐,且异或运算是施加于时钟信号和指令信号上以产生曼彻斯特码。根据ieee 802.3曼彻斯特编码,时钟信号的下降缘与指令信号的转态时间点对齐,且异或运算是施加于时钟信号和指令信号上,接着将异或运算的结果反向以产生曼彻斯特码。根据差分曼彻斯特编码且基于所接收的指令信号,所输出的曼彻斯特码包括高到低和低到高的两种状态。其中,指令信号为“1”代表状态改变;指令信号为“0”代表状态维持不变。

53.请回头参考图5,根据所使用的曼彻斯特编码法,接收器550还可包括一曼彻斯特解码器556_2。曼彻斯特解码器556_2可接收编码后的指令信号,并接着对编码后的指令信号进行解码,使其回复到原始指令信号,同时取出其中的时钟信号。如此一来,原始指令信号和时钟信号即可提供给控制电路558,使得控制电路558可控制接收器550中的电路方块初始化。

54.根据曼彻斯特编码的特性,具有相同频率的原始指令信号和时钟信号可通过曼彻斯特解码器556_2来回复,而无须接收额外的时钟信号或触发信号。曼彻斯特解码器556_2仅需要简易的电路结构,其可包括由数个逻辑闸来实现的延迟方块或计数器,但不限于此。本领域技术人员应熟知关于曼彻斯特解码器556_2的详细实施方式和运作方式,在此不赘述。在另一实施例中,曼彻斯特解码器556_2可包含在控制电路558中,或者与控制电路558互相整合。

55.值得注意的是,本发明的目的在于提供一种新式的信号传输系统,其具备高速数据和低速指令信号传输的能力。本领域技术人员当可据此进行修饰或变化,而不限于此。举例来说,上述实施例是采用曼彻斯特编码法对指令信号进行编码,因此接收器无须使用复杂的时钟数据恢复电路即可进行解码以回复时钟信号和原始指令信号。在另一实施例中,其它类似的编码方式也是可行的。另外,在本发明的实施例中,根据系统需求,可在接收器中选择性地设置或省略终端电路和均衡器,且/或在传输器中选择性地设置或省略输出缓冲器。除此之外,在上述实施例中,指令信号和时钟信号互相结合而通过相同信道传送;但在另一实施例中,若存在多个信道耦合在传输器和接收器之间时,指令信号和时钟信号能够有效使用这些信道,以通过不同信道进行传送。

56.请参考图7,图7为本发明实施例另一信号传输系统70的示意图。如图7所示,信号传输系统70包括一传输器700及一接收器750。传输器700包括一序列化器702及一多路复用器706,其运作方式分别类似于图4中的序列化器402及多路复用器406,故不再详述于此。接收器750包括一终端电路752、一均衡器754、一时钟数据恢复电路756、一控制电路758及一去序列化器760,其运作方式分别类似于图4中的终端电路452、均衡器454、高频时钟数据恢复电路456_1、控制电路458及去序列化器460,故不再详述于此。

57.在此例中,连接于传输器700及接收器750之间的信道是一差分信道,其可用来传送高速差分数据信号序列。当差分数据信号被传送之前,此信道可用来传送低速指令信号序列和相应的时钟信号。差分信道包括两个子信道cha及chb,其中一者用来传送指令信号,另一者则用来在指令信号被传送的同时传送时钟信号。在此例中,子信道cha用于传送指令信号而子信道chb用于传送时钟信号。

58.当接收器750接收到低速指令信号时,因终端电路752、均衡器754及时钟数据恢复电路756尚未完成设定,指令信号可直接由控制电路758接收,控制电路758即可根据所接收的指令信号及其对应的时钟信号来初始化这些电路方块。接着,当这些电路方块初始化之后,代表其已准备好接收和处理高速数据信号。

59.因此,在一数据传输期间,传输器700及接收器750之间的差分信道可用来传送差分数据信号,而在数据传输期间之前的一指令传输期间,差分信道可用来传送指令信号及时钟信号。传输器700及接收器750需对应进行布置以实现上述传输方式。

60.如图7所示,传输器700还包括耦接于多路复用器706的两个输出缓冲器704_1及704_2。详细来说,输出缓冲器704_1耦接于序列化器702和多路复用器706之间,用来输出串行数据信号至多路复用器706,此串行数据信号接着被传送至差分信道。输出缓冲器704_1及多路复用器706之间通过两条连接线互相耦接,这些连接线可用来传送差分数据信号。输出缓冲器704_2耦接于多路复用器706的另一输入端,用来输出串行指令信号及时钟信号至多路复用器706,此串行指令信号及时钟信号接着被传送至差分信道。输出缓冲器704_2及多路复用器706之间通过两条连接线互相耦接,这些连接线分别用来传送两个分开的信号(即指令信号和时钟信号)。因此,多路复用器706可选择传送指令/时钟信号或数据信号至信道上。更明确来说,在指令传输期间,多路复用器706可分别传送指令信号和时钟信号至子信道cha及chb;而在指令传输期间之后的数据传输期间,多路复用器706可传送差分数据信号至子信道cha及chb。

61.接收器750的电路结构类似于图5中接收器550的电路结构,惟接收器750未包括曼

彻斯特解码器。因此,接收器750的控制电路758可通过差分信道直接从传输器700接收指令信号和时钟信号。更明确来说,接收器750可通过子信道cha接收指令信号,并通过子信道chb接收时钟信号。

62.请参考图8,图8为本发明实施例又一信号传输系统80的示意图。如图8所示,信号传输系统80包括两对收发器p1及p2,其中的每一传输器包括一序列化器802、一输出缓冲器804及一多路复用器806,其运作方式分别类似于图4中的序列化器402、输出缓冲器404及多路复用器406,故不再详述于此;每一接收器包括一终端电路852、一均衡器854、一时钟数据恢复电路856、一控制电路858及一去序列化器860,其运作方式分别类似于图4中的终端电路452、均衡器454、高频时钟数据恢复电路456_1、控制电路458及去序列化器460,故不再详述于此。在另一实施例中,多路复用器806也可包含在序列化器802中,或者与序列化器802互相整合。

63.在此例中,收发器对p1中的传输器及接收器通过一信道ch1互相耦接,而收发器对p2中的传输器及接收器通过一信道ch2互相耦接。因此,若设定信道ch1用来传送指令信号时,可设定信道ch2用来在指令信号被传送的同时传送相应的时钟信号。

64.详细来说,在指令传输期间,信道ch1可传送指令信号而信道ch2可传送时钟信号。在指令传输期间之后的数据传输期间,信道ch1及ch2都用来传送数据信号。因此,在传输器端,位于收发器对p1的传输器中的输出缓冲器804和多路复用器806都用来输出一串行指令信号,并接着输出一串行数据信号;位于收发器对p2的传输器中的输出缓冲器804和多路复用器806都用来输出时钟信号,并接着输出另一串行数据信号。在接收器端,收发器对p1及p2的接收器可共用相同的控制电路858,其可从信道ch1接收指令信号并从信道ch2接收时钟信号,从而对每一收发器对p1及p2的接收器中的终端电路852、均衡器854及时钟数据恢复电路856进行起始或设定。

65.本发明的实施例可广泛应用于不同集成电路之间的传输,其信道可以是任何具有高速数据传输能力的晶片间接口,如移动产业处理器接口(mobile industry processor interface,mipi)或集成电路间(inter-integrated circuit,i2c)接口等。

66.综上所述,本发明提供了一种同时具备高速数据及低速指令信号传输能力的信号传输系统。低速指令信号可通过相同信道在高速数据信号之前进行传送。根据指令信号,可对接收器中的电路方块进行设定,以做好接收数据信号的准备。通过适当的时钟信号,可顺利接收指令信号,因此接收器可包括用来处理高速数据信号的高频时钟数据恢复电路,也包括用来处理低速指令信号的低频时钟数据恢复电路或解码器。在一实施例中,可通过类曼彻斯特编码将时钟信息嵌入指令信号,因此解码器可从所接收的指令信号当中取出时钟信息。或者,当指令信号进行传送时,可同时通过另一可用信道来传送时钟信号。举例来说,若传输器和接收器之间设置有一差分信道时,此差分信道的一子信道可用来传送指令信号,另一子信道可用来传送时钟信号。在又一实施例中,可采用两对收发器(传输器加上接收器)来分别传送/接收指令信号和时钟信号。因此,根据本发明的实施例,指令信号(搭配相应的时钟信号)可通过现有的信道进行传送,而无须使用额外的时钟端口,可降低电路面积和成本。

67.以上所述仅为本发明的优选实施例而已,并不用于限制本发明,对于本领域的技术人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修

改、等同替换、改进等,均应包含在本发明的保护范围之内。

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!

1